About wiring decoupling capacitors

As you know, the speed and density of digital logic circuits double every three years. Between 1974 (announcement of the 8080 processor) and 2014, the speed of typical microprocessor operations increased from 200 kHz to 2000 MHz. This is a general trend in the electronics industry, and it is adamant: consumers demand ever-faster performance.

If the speed has changed so much, then we can assume that the role of the decoupling capacitor could also increase enormously. However, it is not. This unassuming component is applied in the same way and for the same tasks as in the seventies. It is time for a change.

Why are changes needed?

Due to the high speed of logic elements, the spectrum of a typical digital signal is in the gigahertz range. Therefore, the frequency characteristics of the isolation components used as protection of the battery against fluctuations caused by switching signals should overlap this range. Yesterday’s rules for designing electronic circuits and printed circuit boards for relatively low-frequency devices are completely unacceptable today when developing high-speed circuits.

The main symptom of the use of inappropriate outdated decoupling capacitors is increased power source noise, increased crosstalk, and large electromagnetic radiation. High-frequency isolation of power sources is a significant issue that deserves a serious attitude towards yourself.

Electrical characteristics of decoupling capacitors

The overall characteristics of the decoupling capacitors depend on their electrical and mechanical parameters. The main electrical problem is the presence of a parasitic series inductance in a real capacitor. As the frequency increases, the impedance of this inductance increases and, eventually, begins to become the dominant characteristic of the component.

In the most critical frequency range from 100 to 1000 MHz, the efficiency of a typical decoupling capacitor is almost entirely determined by its series inductance. These frequencies are widely used in logic circuits (see Note). To obtain good electrical characteristics, it is necessary to reduce the series inductance, which is mainly determined by the contact pads of the capacitor and the associated openings (including transient). Every time when the frequency of the edges of a pulse signal is doubled, our dependence on these elements of the printed circuit board doubles.

The increase in the parasitic series inductance is associated with the following factors:

1. a large length of conductors (> 0.25 mm) between the terminals of the capacitor and the holes,

2. vertical mounting on a printed circuit board

3. using types other than those intended for surface mounting

4. small diameter of vias pads (<0.9 mm)

On the other hand, parasitic series inductance can be reduced if the following rules are observed:

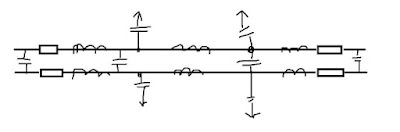

1. use types of capacitors designed for surface mounting, using short and wide contact pads with vias, located directly on these pads without connecting conductors

2. using design of large diameters of vias

3. the use of thin printed circuit boards (thickness less than 0.75 mm) for a shorter power supply and ground to the capacitor. Parasitic sequential inductance is quite real and measurable. A printed circuit board containing only decoupling capacitors, with the help of the analyzer, you can try to investigate the dependence of the impedance of the power-to-ground signals on the frequency. The graph of dependence will have a pronounced region near the frequency of 1 MHz with a reduced impedance. In this area decoupling capacitors perform their function in the best way.

Further, with increasing frequency, the impedance increases to a maximum value in a region of about 100 MHz. In this region, the parasitic sequential inductance, which, as noted earlier, depends on the PCB layout, has a dominant effect.

At higher frequencies (1000 MHz and higher), the impedance relationship has several maxima and minima. In this frequency domain, the natural capacity between the layers of power and the ground, if any, of course, is decisive. Such interlayer effects for most practical applications can be considered manifestations of an ideal capacity.

If the printed circuit board has too much noise in the frequency range from 100 to 1000 MHz, the most effective solution to this problem will be to improve the wiring of decoupling capacitors and vias, reducing to reducing the parasitic inductances of the leads and conductors. If it is impossible to improve the wiring, you can advise the following:

1. add decoupling capacitors to the board,

2. replace the existing decoupling capacitors with higher-frequency ones (with a dielectric with a smaller dielectric loss tangent),

3. reduce impulse currents by reducing the load of each logic element or reducing the number of simultaneously switching elements.

In the end, you can try to use as a substrate for a printed circuit board material with a higher dielectric constant, which will increase the capacitance between the layers of power and the ground, or, for multilayer printed circuit boards, make these layers adjacent, which is a generally accepted rule. The latter options allow to reduce the power-to-ground impedance at frequencies above 500 MHz.

Conclusion

Proper wiring of the junction circuits plays a crucial role in solving the problem of power and ground noise, reducing crosstalk and electromagnetic radiation. With increased noise in the range from 100 to 1000 MHz, the problem may be incorrect wiring of decoupling capacitors, creating additional parasitic series inductance.

Note

The frequency range of the pulse signal, which is a function of its rate of rise, and not the repetition frequency, extends from zero to a frequency equal to half the reciprocal of the signal front time (from 10 to 90%). For example, the frequency range of a pulse signal with a front of 1 ns exceeds 500 MHz.

Comments: 0

Post a Comment